# **EE2013**

## **NON-LINEAR CIRCUIT ANALYSIS**

**LECTURE 19: OPAMP POSITIVE FEEDBACK**

Instructors: Alex Jaeger, Anthony Wall Coordinator: Prof. Pádraig Cantillon-Murphy

# LECTURE SCHEDULE

Thursdays 11am-1pm (with short break)

Monday 9am-10am slot not used!

# LECTURE NOTES

https://www.jaeger.ie/ee2013/lec17

Uploaded before lecture takes place

# **QUESTIONS?**

Just ask whenever it comes to you!

OR:

anthony.wall@mcci.ie on Email, Teams or Canvas

### 1 Review from Last Time

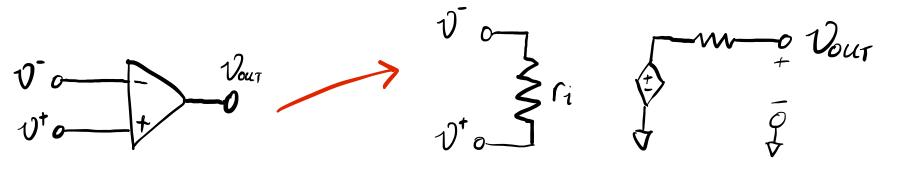

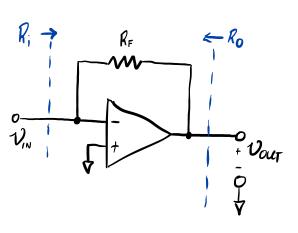

## 1.1 Op Amp Input and Output Resistance

To analyse the input and output circuit resistance in op amp circuits, we need to add a test source and improve the model of the op amp by adding internal input  $(r_i)$  and output  $(r_o)$  resistances.

This improved model allows us to calculate the input and output resistance given here for the inverting op amp amplifier:

$$R_i = R_S + \frac{R_F + r_o}{A} \approx R_S$$

Commant

The input resistance should be dominated by the series input resistance.

$$R_o = \frac{r_o}{1 + A\frac{R_S}{R_S + R_F}} \approx \frac{r_o(R_S + R_F)}{AR_S} \frac{1}{A > 71}$$

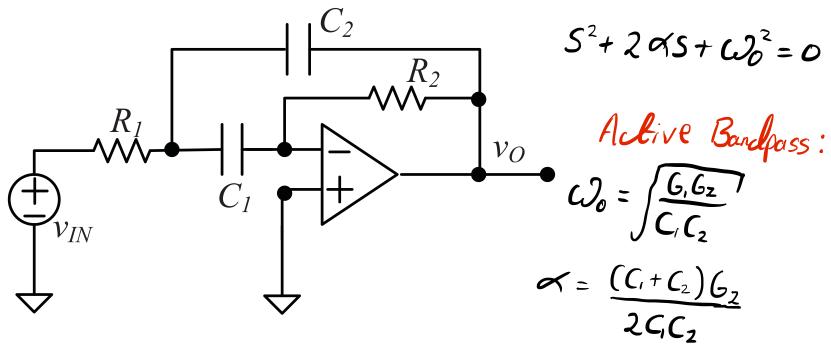

### 1.2 Active Op Amp Filters

Active op amp filter circuits, like the bandpass filter below, eliminate the need for planar inductors in high-current VLSI circuits.

#### 2 Positive Feedback and Op Amps

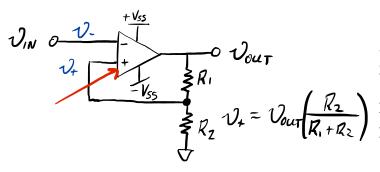

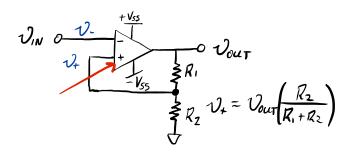

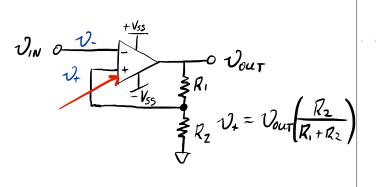

$\mathcal{V}_{\text{out}} = \mathcal{A}(\mathcal{V}_{\text{i}} - \mathcal{V}_{\text{o}})$ To date, we have only considered op amp circuits with negative feedback. However, what happens to the non-inverting amplifier circuit if we switch the input terminals to create positive feedback?

In this configuration, the op amp is bistable because once  $v^+ - v^-$  becomes slightly positive (negative) the op amp immediately saturates to  $+V_S(-V_S)$  due to the large positive gain, A. The op amp remains at  $+V_S(-V_S)$  until  $v^+ - v^-$  becomes negative (positive).

In the circuit shown,  $v^- = v_{IN}$  so the condition for positive saturation assuming that the op amp is initially negatively saturated becomes:

$$A(v^{+} - v^{-}) = A(-\frac{V_{S}R_{2}}{R_{1} + R_{2}} - v_{IN}) > 0 \quad \text{-}V_{SS} = -V_{S}$$

For  $R_1 = R_2 = R$ :

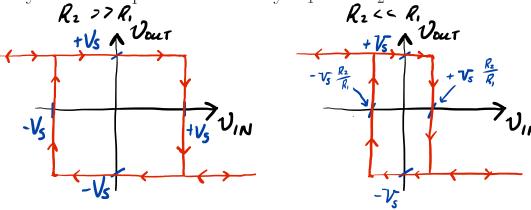

Since A is positive,  $v_{IN} < -\frac{V_S}{2}$  changes the output from negative  $(-V_S)$  to positive  $(+V_S)$  saturation. The output remains in this state until  $v_{IN} > \frac{V_S}{2}$ , at which point, the output again reverts to  $-V_S$ .

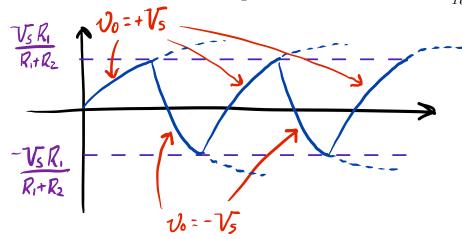

The phenomenon by which the output depends on the past input as well as the present input is known as *hysteresis*. Hysteresis results in the loop in the  $v_{IN} - v_O$  relation where the width of the hysteresis loop is controlled by  $R_1$  and  $R_2$ .  $R_2 > R_1$   $R_2 < R_1$

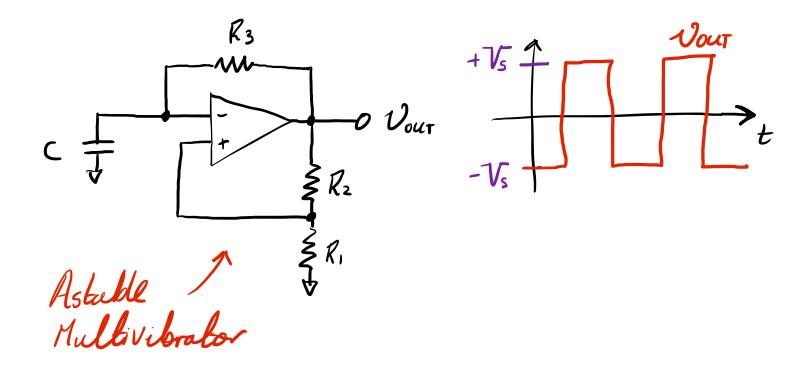

### 3 The Op Amp Voltage Oscillator

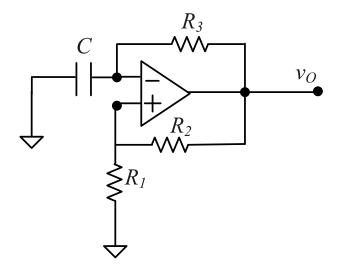

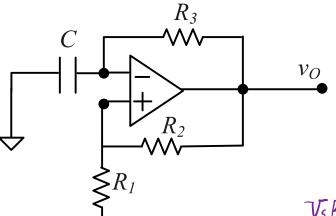

Positive feedback results in op amp saturation, which is useful is some situations. By including RC elements, we can use positive feedback to design a voltage oscillator.

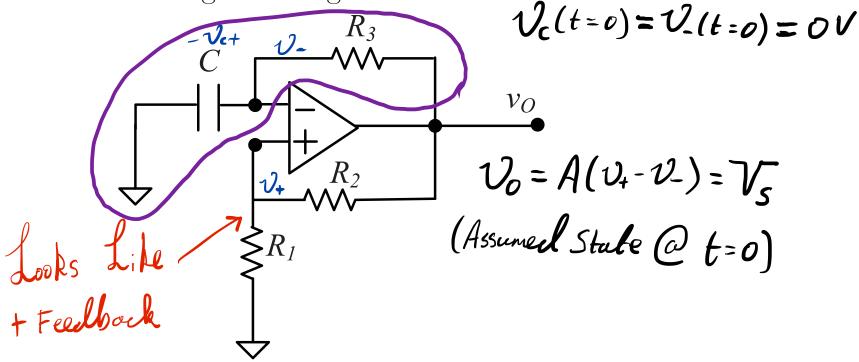

With the capacitor initially in the uncharged state  $(v_C = v^- = 0)$ , the output is positive:  $v_O = A(v^+ - v^-) = V_S$ .

$$\mathcal{O}_{+} = \mathcal{V}_{o} \frac{R_{i}}{R_{i} + R_{2}} = \mathcal{V}_{s} \frac{R_{i}}{R_{i} + R_{2}}$$

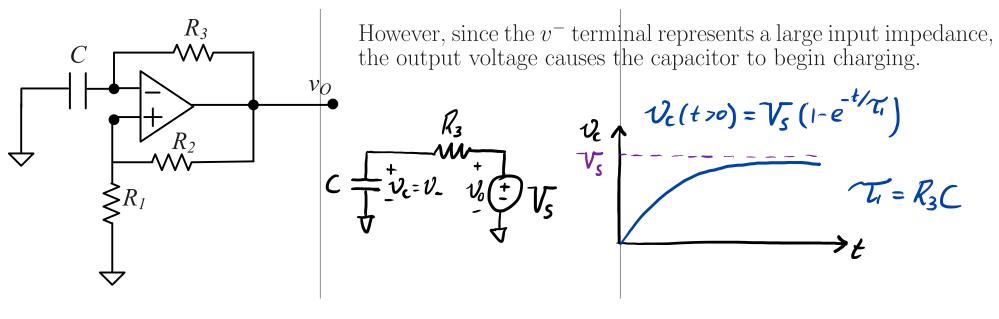

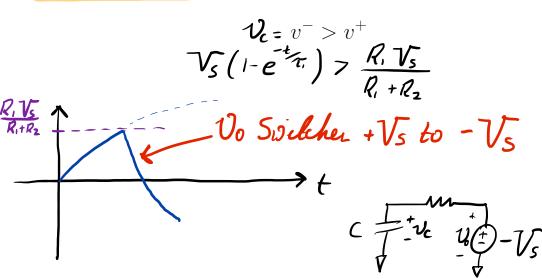

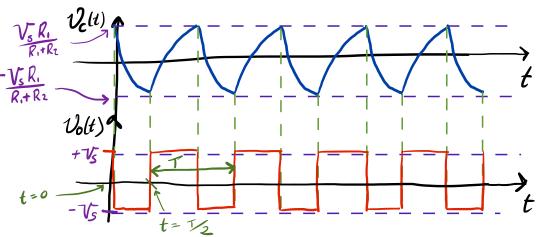

As the capacitor charges,  $v_C = v^-$  will eventually exceed  $v^+ = \frac{R_1 V_S}{R_1 + R_2}$  resulting in the output,  $v_O = A(v^+ - v^-)$ , switching from positive  $(+V_S)$  to negative  $(-V_S)$ . This happens when:

Once the output changes to  $-V_S$ , the positive input,  $v^+$ , also changes:

$$v^{+} = \frac{R_1 v_O}{R_1 + R_2} = -\frac{R_1 V_S}{R_1 + R_2}$$

Now, the partially charged capacitor has a higher voltage than the output voltage and begins to discharge through  $R_3$ . The capacitor continues to discharge until  $v_C = v^- = -\frac{V_S R_1}{R_1 + R_2}$

As soon as the capacitor voltage then exceeds  $-\frac{R_1V_S}{R_1+R_2}$ , this causes  $A(v^+-v^-)$  to turn positive and the op amp returns to positive saturation:

$$V_0 = + V_S$$

$$V_+ = \frac{R_1 V_S}{R_1 + R_2}$$

The capacitor then begins charging again and so on, the process repeating itself everytime that the capacitor voltage satisfies the condition:

$$\frac{1}{V_{c}(t)} = \pm \frac{V_{s} k_{1}}{R_{1} + R_{2}}$$

$$\frac{1}{V_{s} R_{1}} \frac{1}{R_{1} + R_{2}}$$

#### 3.1 Oscillator Time Constants

An important parameter is the oscillation period, T, which depends on the component values. To determine T, consider the discharging cycle of the capacitor:

$$V_c(t=0^-) = V_c(t=0^+) = \frac{V_s R_i}{R_i + R_2}$$

Since  $v_O = -V_S$  at  $t = 0^-$ , the final possible capacitor voltage at  $v_C(t \gg \tau_1)$  is  $-V_S$ . In general:

$$v_C(t) = v_C(0^+)e^{-t/\tau} + v_C(t \gg \tau)(1 - e^{-t/\tau})$$

$$\Rightarrow v_C(0 < t < T/2) = \frac{V_s R_1}{R_1 + R_2} e^{-t} + (-V_s) \left(1 - e^{-t} \right)$$

The output voltage switches from  $-V_S$  to  $+V_S$  at t=T/2, at which point:

$$v_C(t = T/2) = \frac{R_1 V_S}{R_1 + R_2} e^{-T/(2\tau_1)} - V_S + V_S e^{-T/(2\tau_1)} = \frac{-V_S R_1}{R_1 + R_2}$$

$$e^{-1/2\tau_{1}\left(\frac{R_{1}}{R_{1}+R_{2}}+1\right)=1-\frac{R_{1}}{R_{1}+R_{2}}}$$

$$\frac{R_{1}+R_{2}}{R_{1}+R_{2}}$$

$$e^{-\frac{1}{2}\tau_{1}}\left(\frac{R_{1}+R_{2}+R_{1}}{R_{1}+R_{2}}\right) = \frac{R_{2}}{R_{1}+R_{2}}$$

$$e^{-T/(2\tau_{1})} = \frac{R_{2}}{2R_{1}+R_{2}}$$

$$-\frac{1}{2T_1} = \ell_1\left(\frac{R_2}{2R_1+R_2}\right)$$

$$\frac{T}{2\tau_1} = \ln(\frac{2R_1 + R_2}{R_2}) = \ln(\frac{2R_1}{R_2} + 1)$$

$$T = 2T_1 \operatorname{Cn}\left(\frac{2R_1}{R_2} + 1\right)$$

$$T = 2R_3C \ln(\frac{2R_1}{R_2} + 1)$$

This is the simplest op amp oscillator design and is the basis for the 555 timer IC.