## **MOSFETs Part 11: Saturation**

Tuesday 24 March 2020 09:54

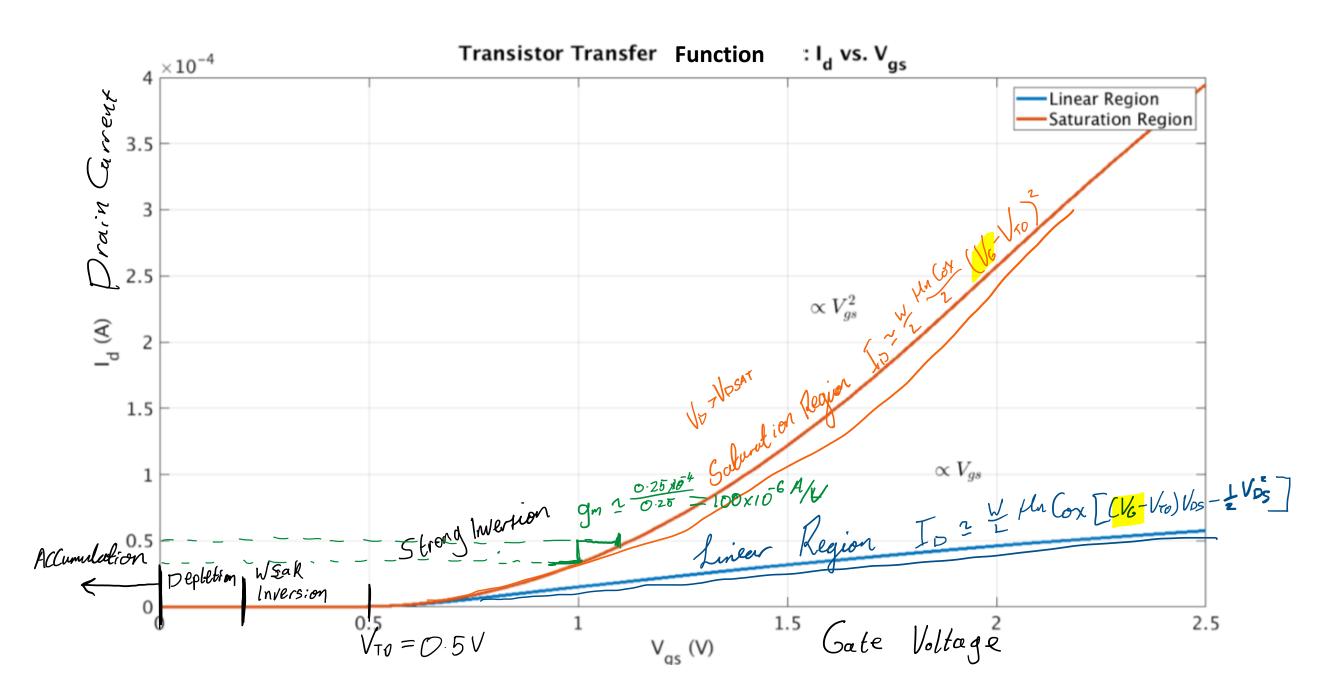

- The previous section shows that for high  $\sqrt{DS}$ , current will decrease

- This doesn't make sense ٠

- Rather than the current starting to decrease, the ٠ device enters what is called the saturation region

Understanding the Saturation Region

Io

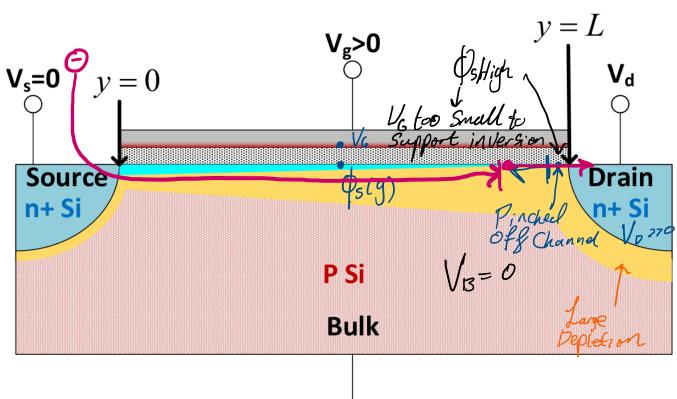

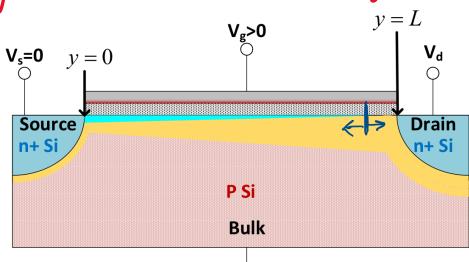

- When the Drain Voltage  $V_{\mathcal{D}}$  becomes large, the P-Bulk n+drain P-N Junction becomes heavily reverse Biased

- A large Depletion region forms around the drain ٠

- The Drain Voltage can become so large that the inversion charge is repelled

- This happens when the gate Voltage is no longer large • enough to hold the inversion charge in place

- But if there's no inversion channel, how can current still • flow?

- Electrons are carried from the source through the channel to the end of the inversion channel

- The electric field in this region is very high due to the high Drain Voltage

- The distance between the end of the Channel and the drain is very small

- The electrons are swept across the junction in a similar way to how minority carriers are swept across the base in a BJT

V<sub>b</sub>=0

y = L

$V_{d}$

Mathematically Describing Saturation v = Surface Potential is given by: V = 0 v = 0

• The Surface Potential is given by:

$\Phi_{s}(y) = 2\Phi_{F} + V(y)$

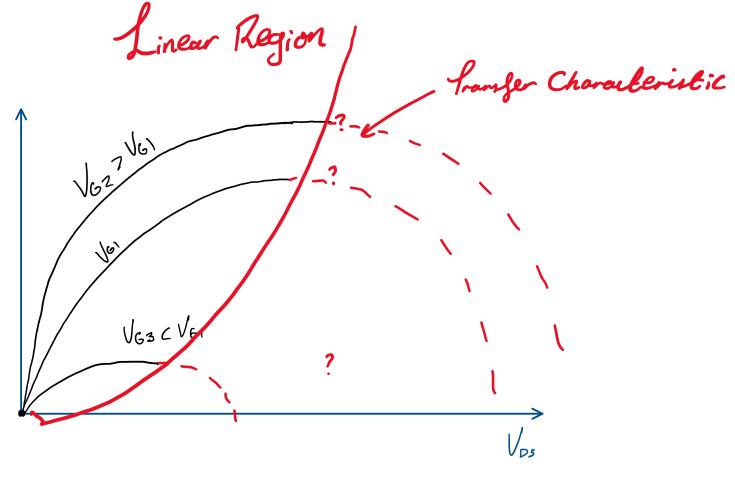

Transfer Junction

9

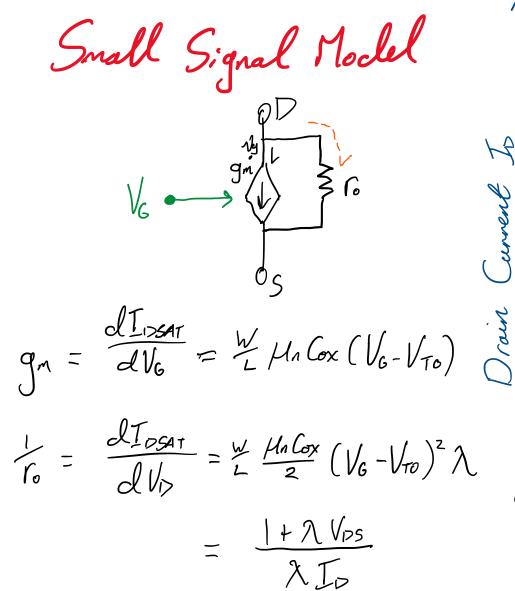

9m 10 Vallage VG Gale Length Modulation Effect honnel J

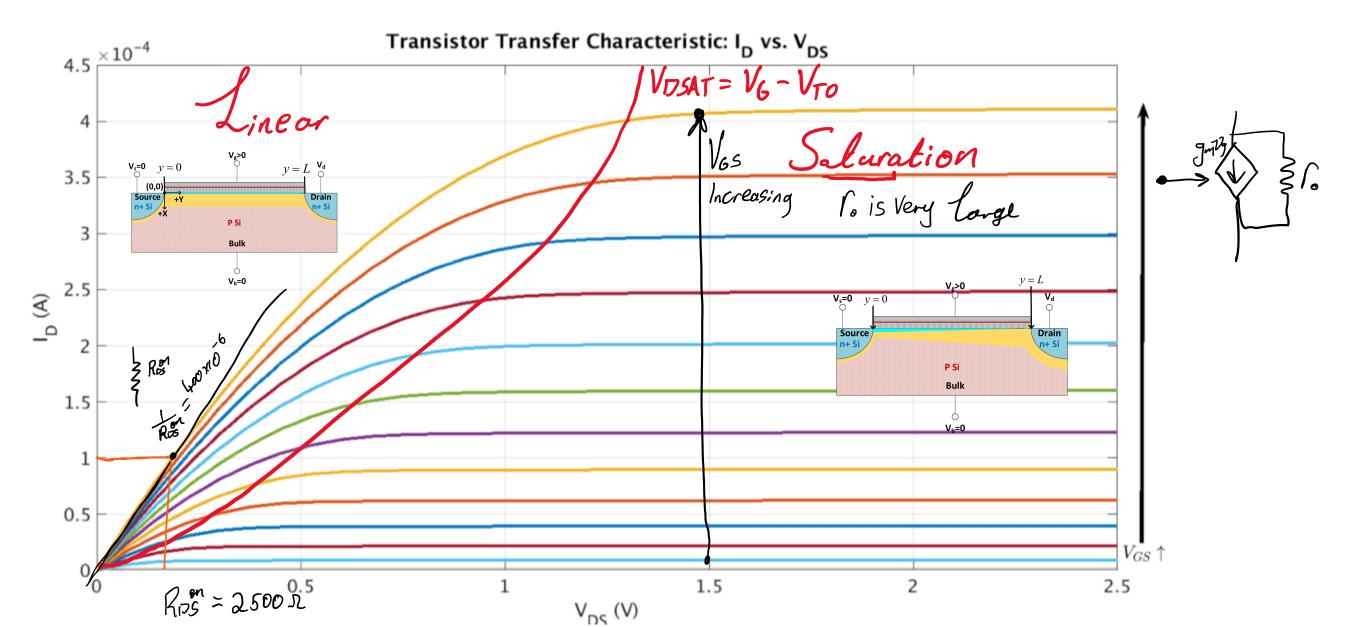

- In real devices, the end of the channel varies slightly with changing Drain Voltage  $\Delta | /_{D}$

- This introduces a \*slight\* dependence on  $V_{\mathcal{P}}$ :

- We model this with  $\mathcal{A}$ , the channel length modulation parameter:

$$\int_{D_{SAT}} \frac{1}{L} \frac{W}{L} \frac{\mu_n Cox}{2} \left( \left( V_G - V_{TO} \right)^2 \left( 1 + \lambda V_D \right) \right)$$

The Saturation current now lightly depends on Drain Voltage. We • model this as a resistance in series with the controlled current source:

Ó

$$V_{DS4T}$$

$$V_{D}=V_{G}-V_{TO}$$

$$V_{b}=0$$

Drain Vallage Vo

Let's Analyse A Real Device A Standard 65 nm device (NMOS Core) R.g. Intel Core 2 Duo, Xbox 360 Opus CPU, iPhone 36s GU